Projects

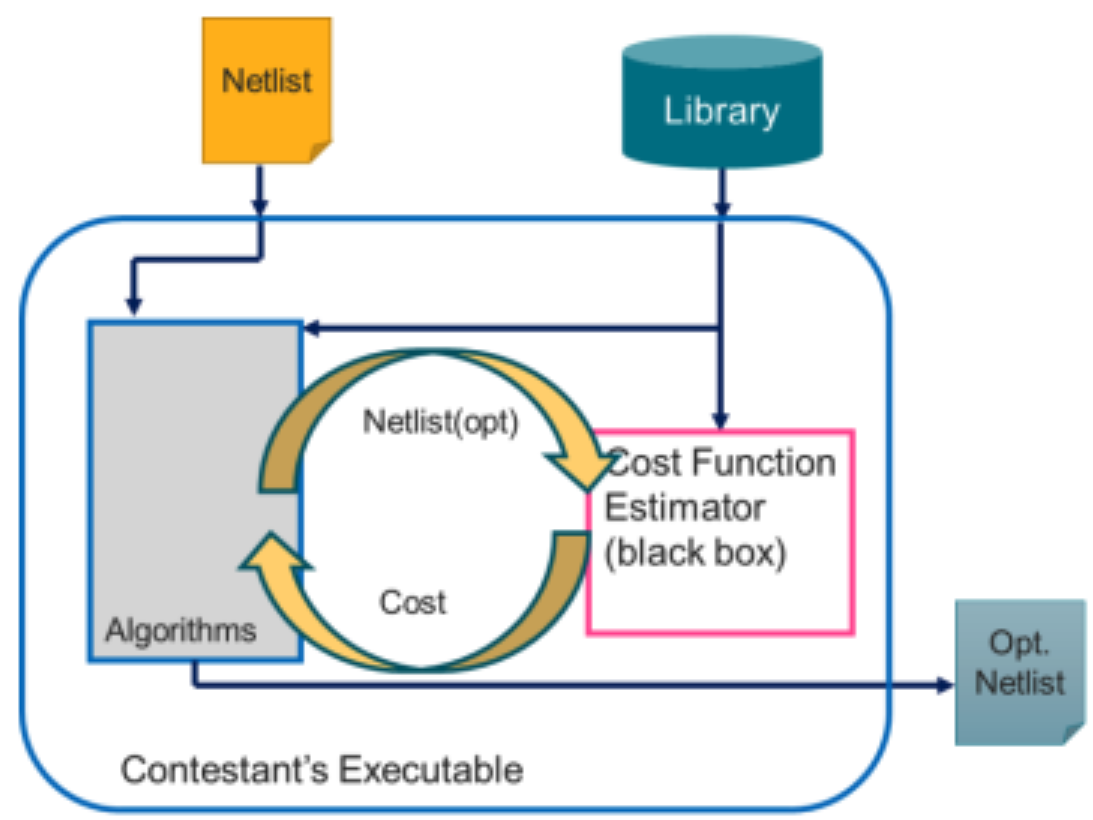

Reinforcement Logic Optimization for a General Cost Function

- Developed a program to optimize digital circuits based on a black-box cost estimator, addressing complex optimization beyond traditional PPA metrics.

- Implemented the A2C reinforcement learning algorithm and Simulated Annealing on Yosys-ABC for circuit optimization, achieving up to 55.3% improvement in loss compared to the Greedy algorithm.

Image reference: ICCAD Contest 2024

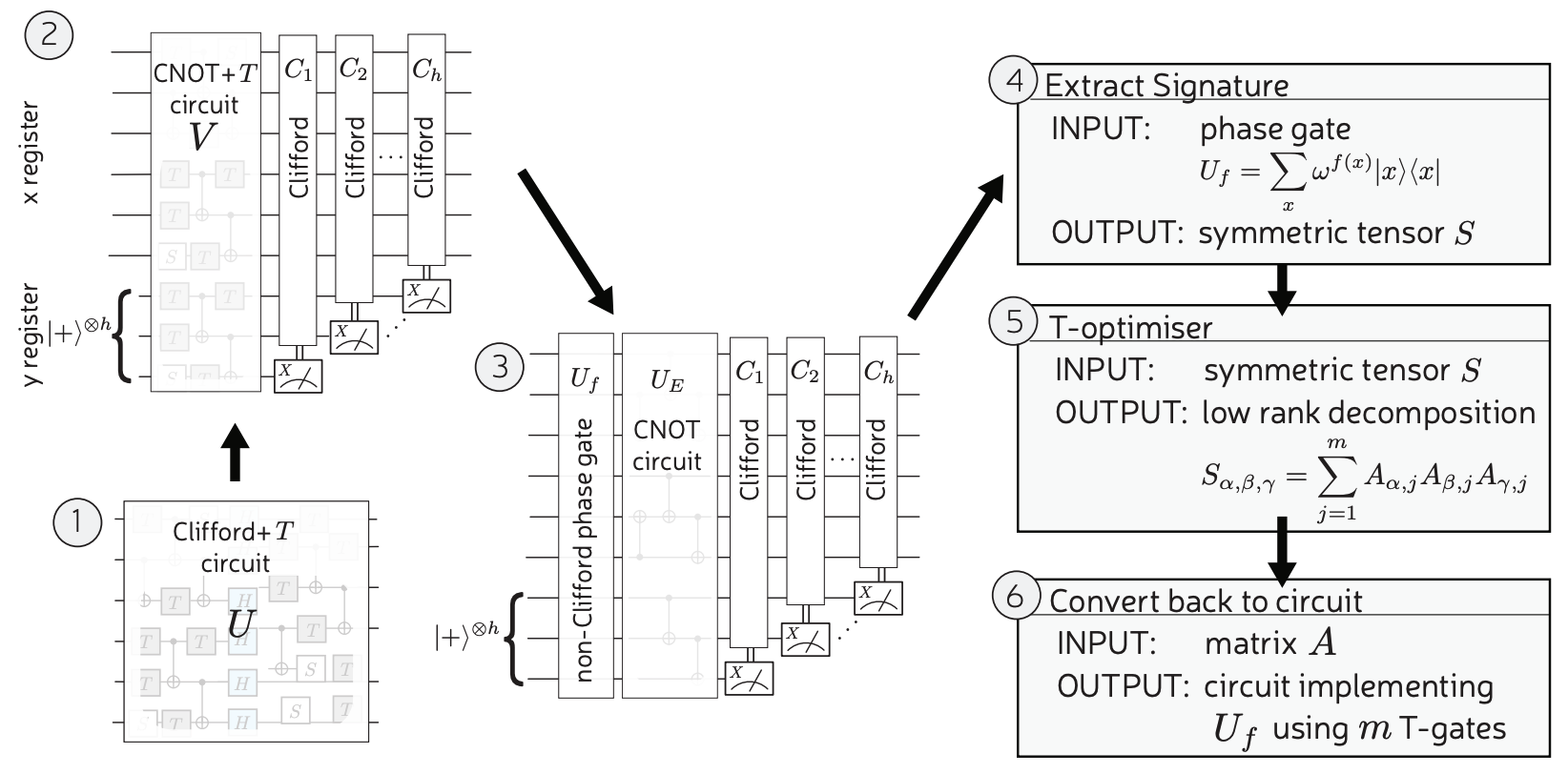

T-Count Optimization Framework for Clifford+T Quantum Circuits

- Developed a unified T-count optimization framework that integrates multiple reduction techniques including TMerge, Internal-H-OPT and advanced phase polynomial methods such as TODD for efficient circuit synthesis.

- Enhanced overall circuit efficiency by combining Gray synthesis (GraySyn) with T-parallelism (T-Par) strategies to exploit structural regularities and gate-level concurrency.

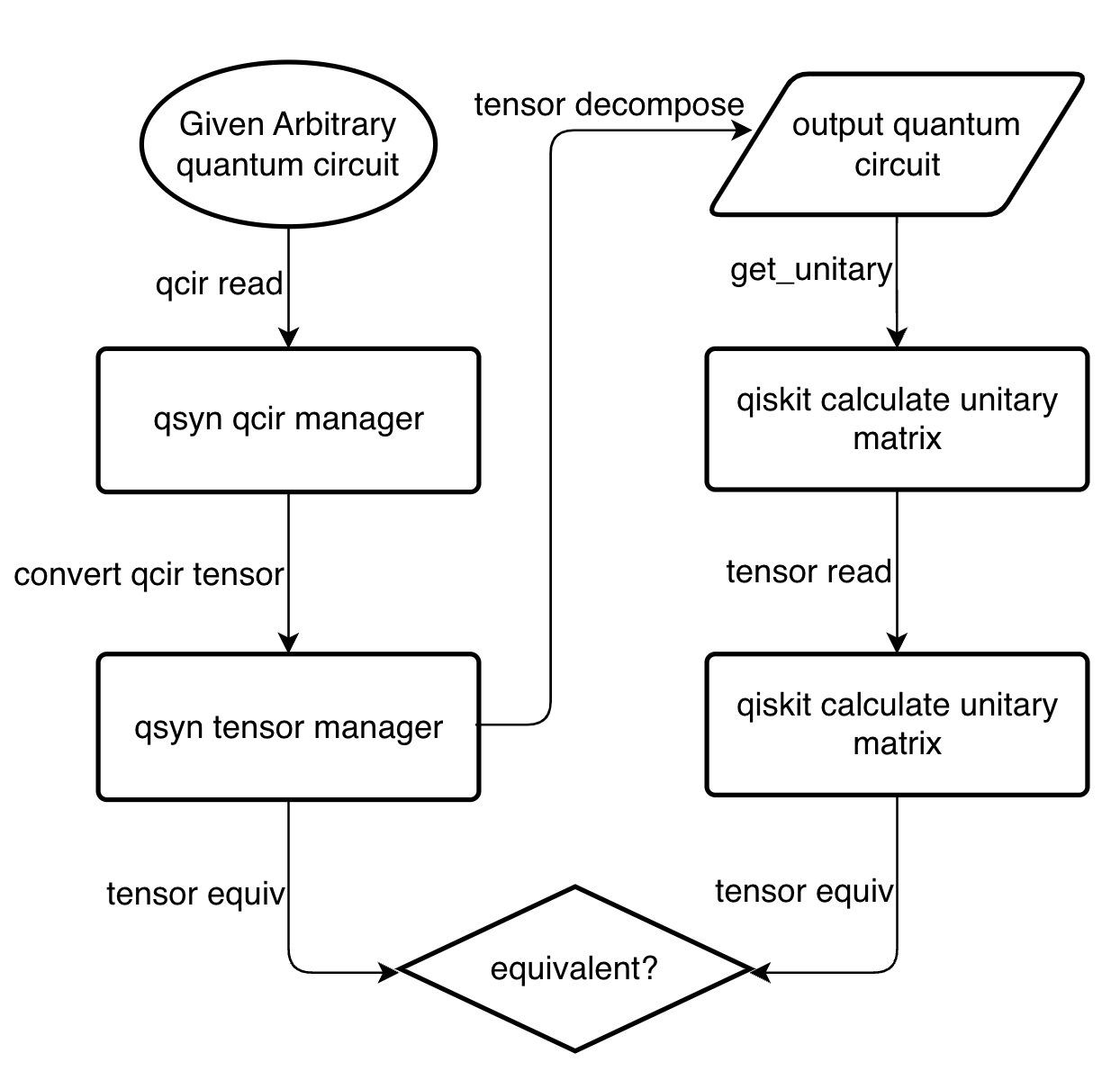

Quantum Circuit Enumeration with Unitary Matrixt

- Read in a valid unitary matrix, converting the tensor into several 2-level matrices.

- Use gray-code synthesis to map the matrices into quantum gates, decomposing and optimizing to get the final quantum circuit with the given basic gate sets.

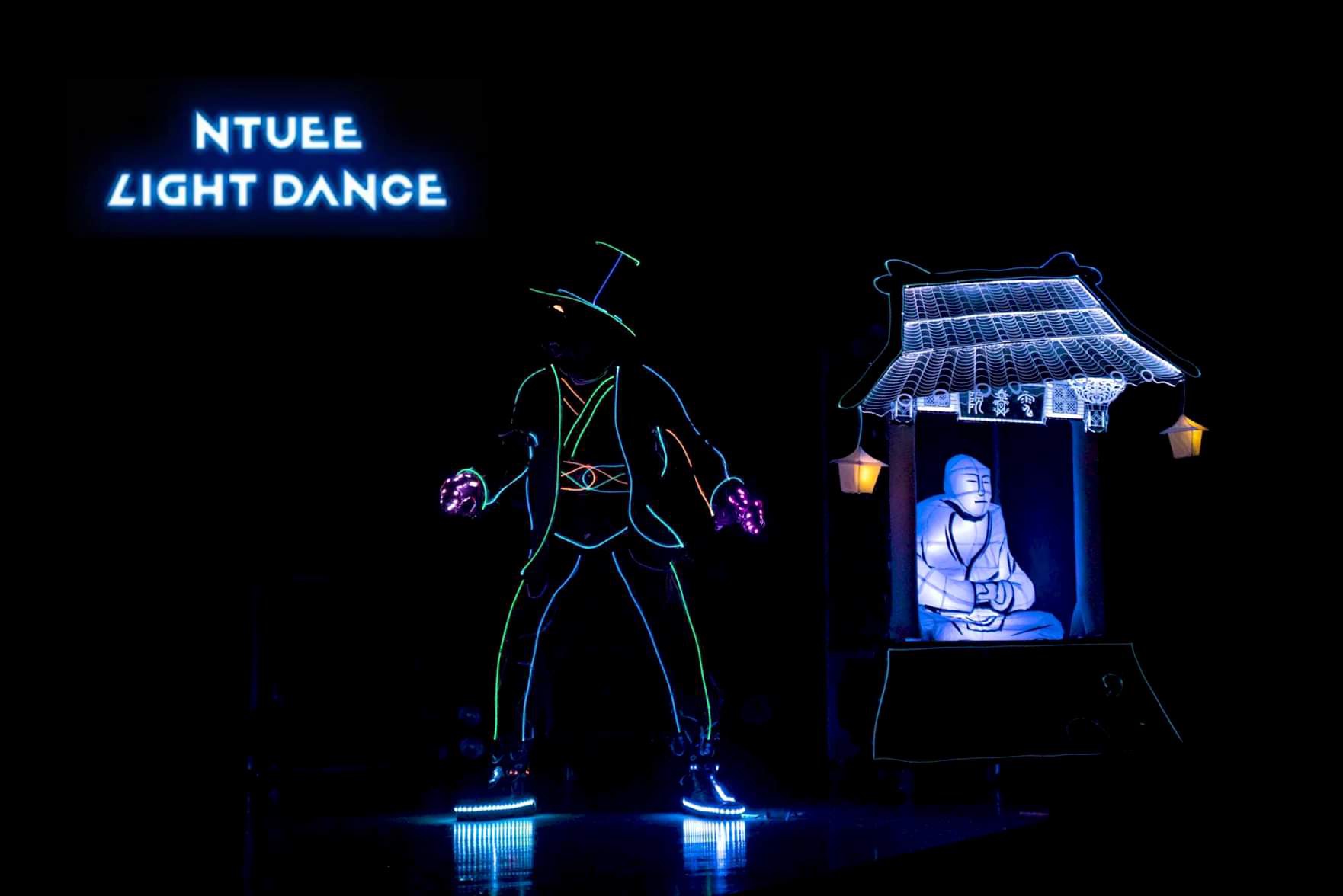

NTUEE LightDance

- Established a C/C++ library for the communication between ATTiny85 board and RPI.

- Constructed the full data path from the latch to the microcontroller and then to the Raspberry Pi for WS2812 LED strips, and from the PCA9955 IC to the Raspberry Pi for optical fiber.

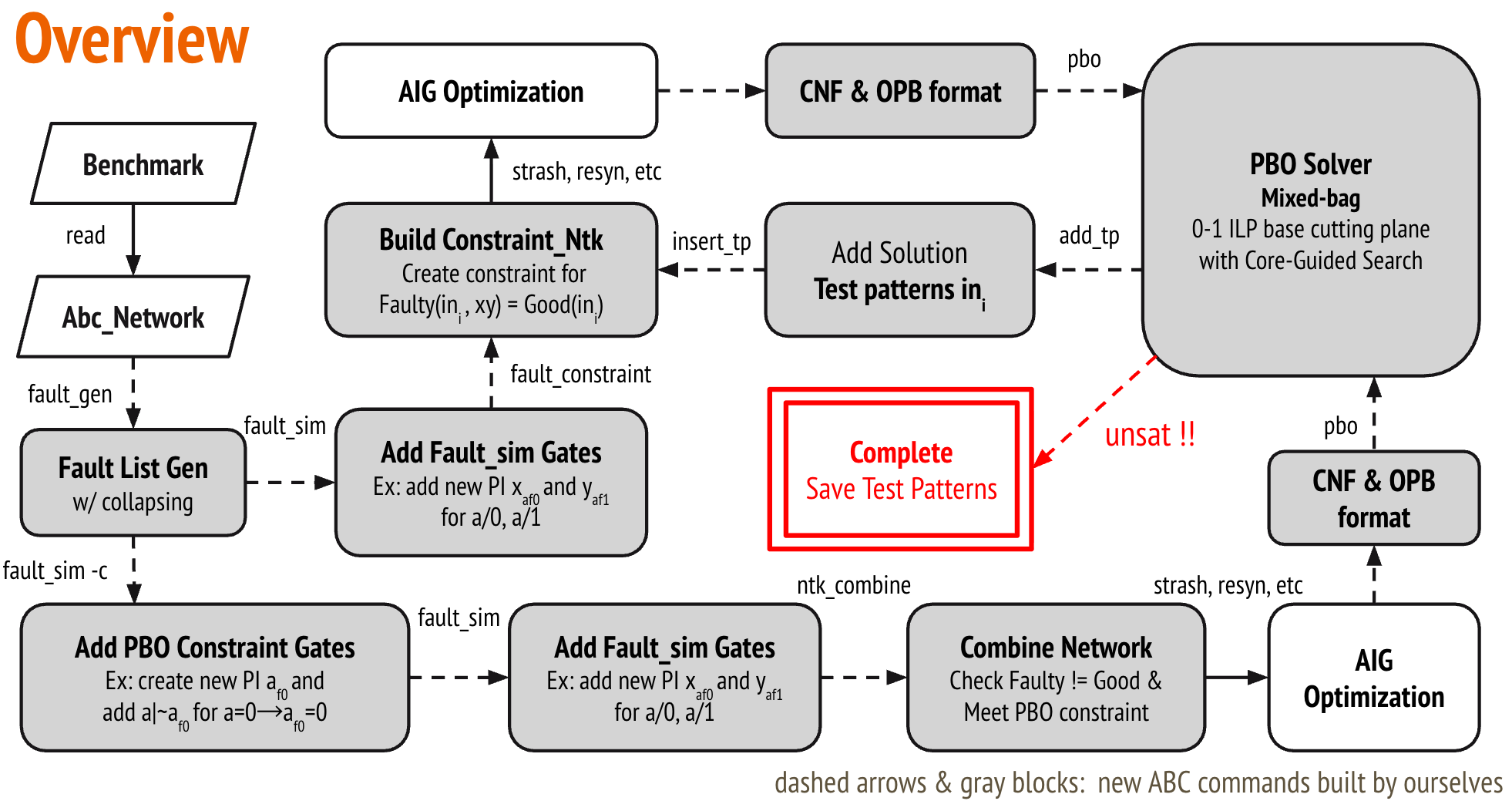

Improved SAT-based ATPG on ABC: Incremental PBO with better compaction

- Developed an incremental SAT-based ATPG framework using Pseudo-Boolean Optimization (PBO) to minimize pattern count and runtime, achieving improved compaction efficiency.

- Encoded complete fault lists into a single SAT instance with structural Boolean objectives, enabling selective pattern generation and extensibility to fault diagnosis.

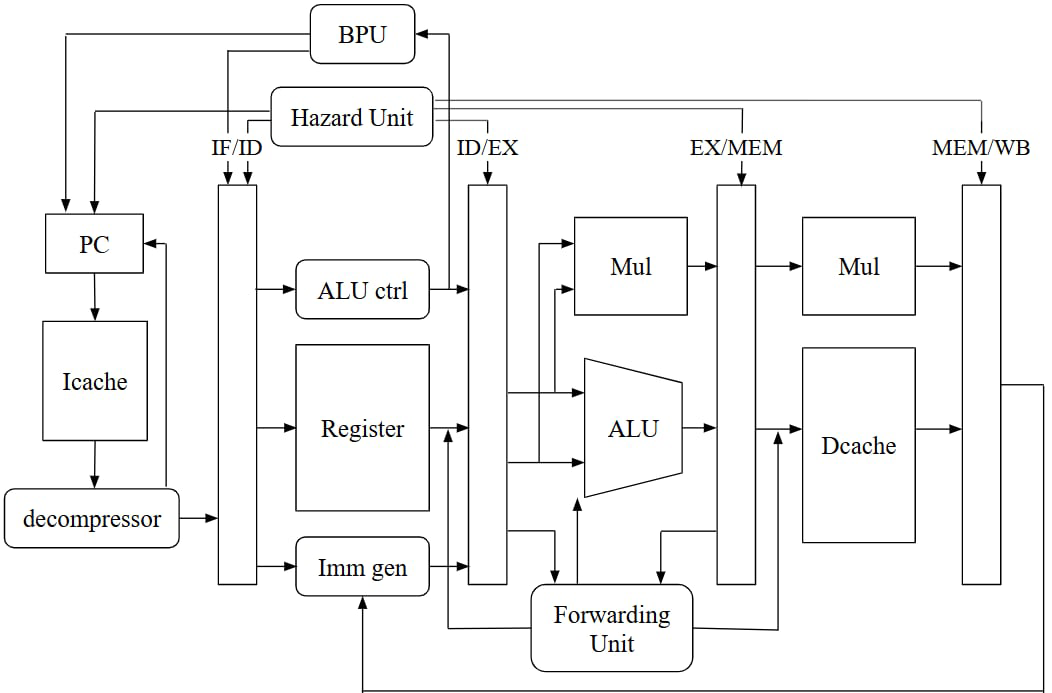

Pipelined RISC-V Processor

- Designed a 32-bit, 5-stage pipelined RISC-V processor supporting the RV32I base and C extension, integrating instruction/data caches and custom control logic for efficient pipeline execution.

- Integrated a decompression unit for 16-bit instructions and a two-stage pipelined multiplier, improving execution efficiency by up to 37% with minimal area overhead.

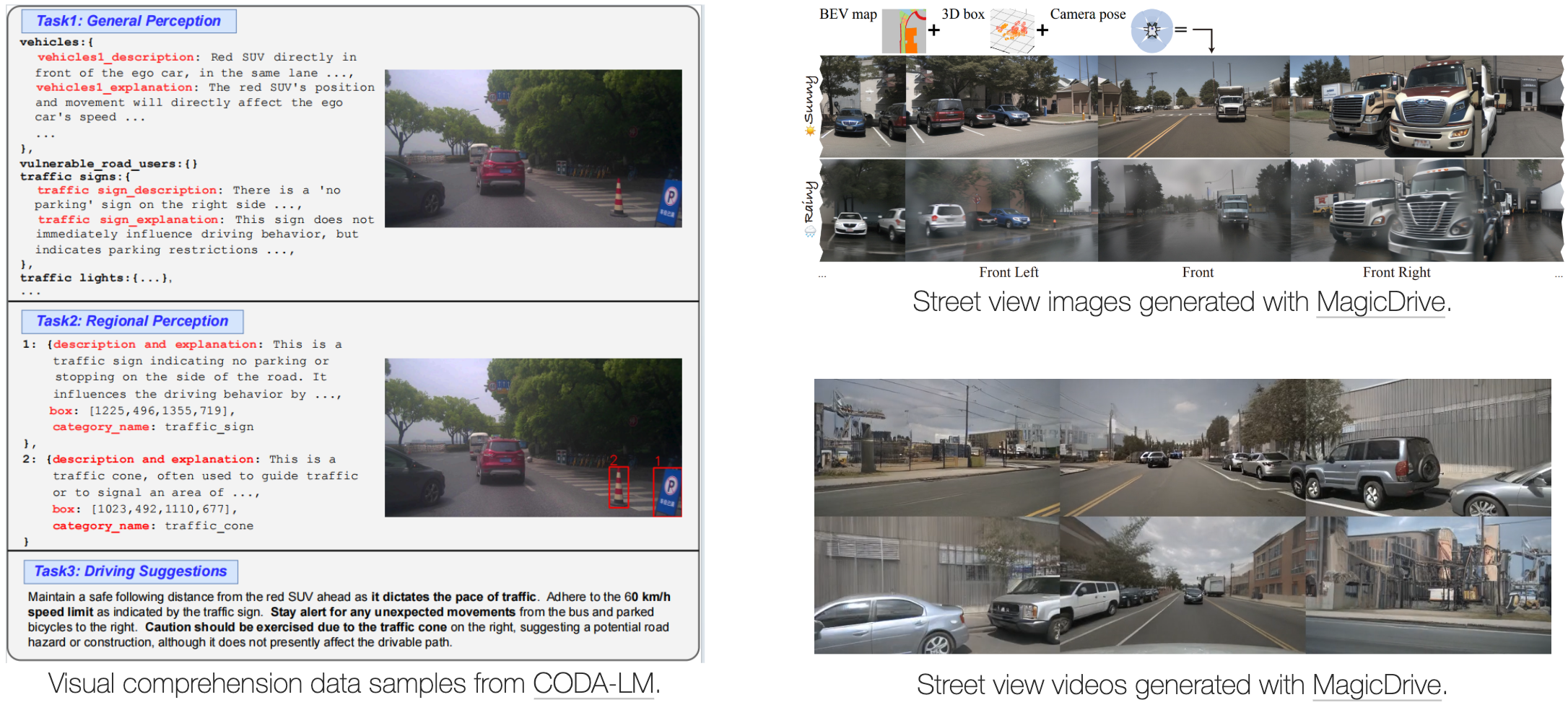

Multimodal Perception of Corner Cases in Autonomous Driving

- Developed a system for multimodal perception and comprehension in autonomous driving, focusing on global scene understanding, local area reasoning, and actionable navigation using the CODA-LM dataset.

- Enhanced the perception capabilities of LLaVA 1.5 7b by fine-tuning LoRA and incorporating additional modules to handle diverse scenes, small objects, and complex driving scenarios effectively.

Image reference: CODA 2024 Workshop

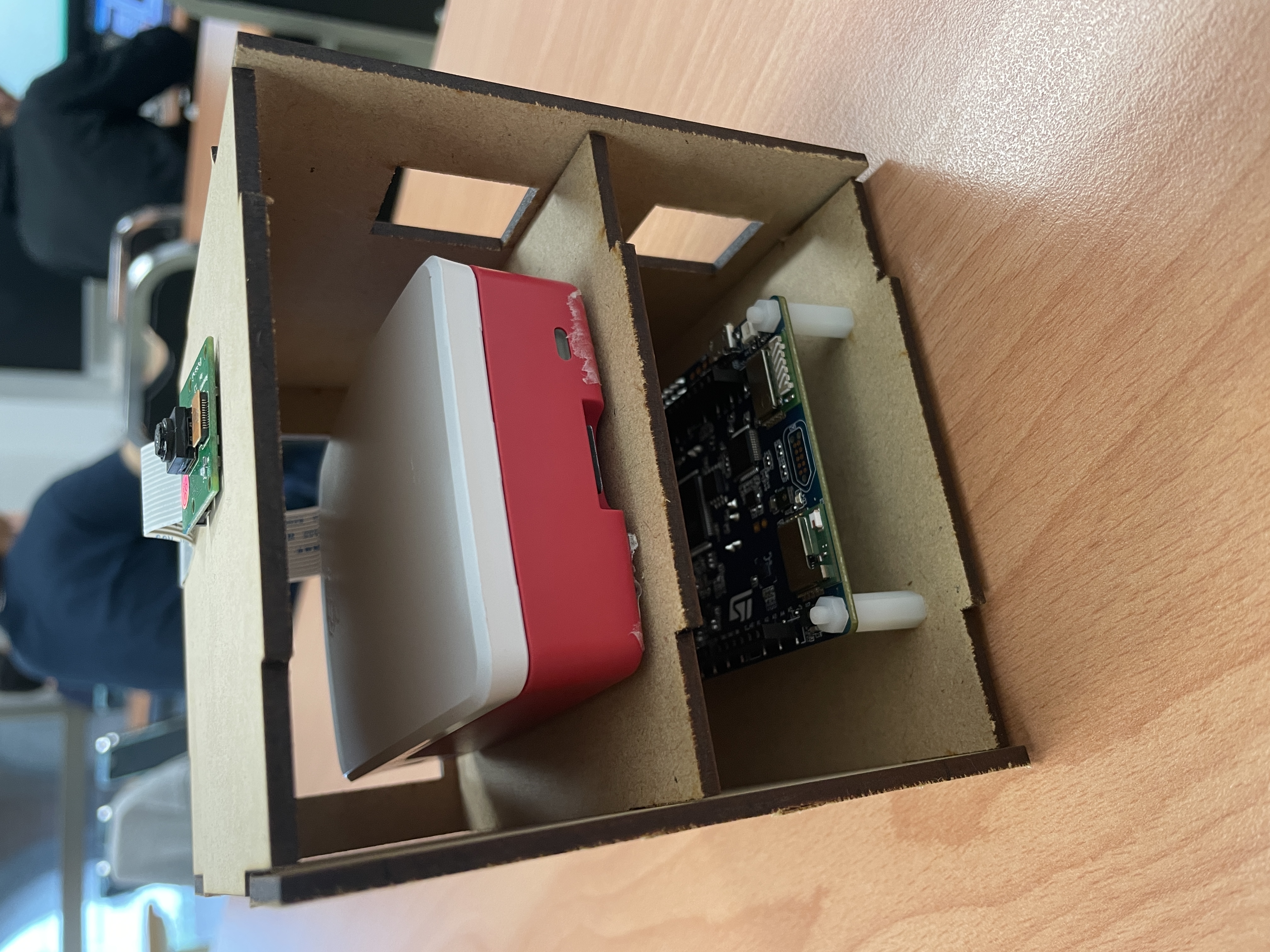

Smart Meeting Cube: Embedded System for Interactive Meeting Management

- Designed a Smart Meeting Cube that streamlines meeting management tasks such as attendance, voting, and speaking requests through interactive cube rotations.

- Implemented face recognition and real-time communication between STM32 and Raspberry Pi using WebSocket.