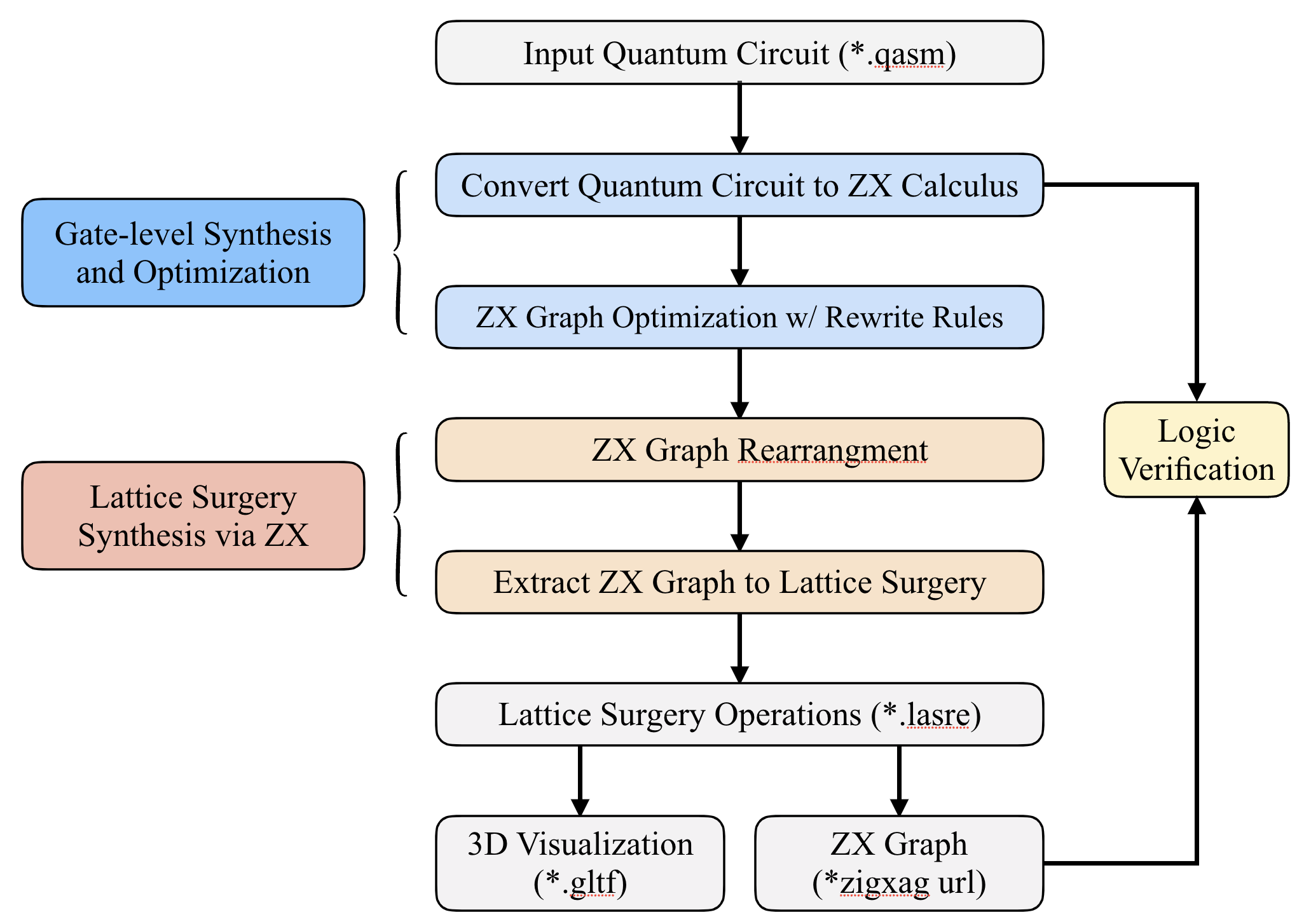

A Novel Ultra-Low Logic Step Fault-Tolerant Quantum Circuit Synthesis via Lattice Surgery

Chien-Tung Kuo, Cheng-En Tsai, Chung-Yang (Ric) Huang

A novel quantum circuit synthesis framework that converts quantum circuits to ZX Calculus, optimizes them, and produces fault-tolerant lattice surgery operations with 3D visualization and verification capabilities.

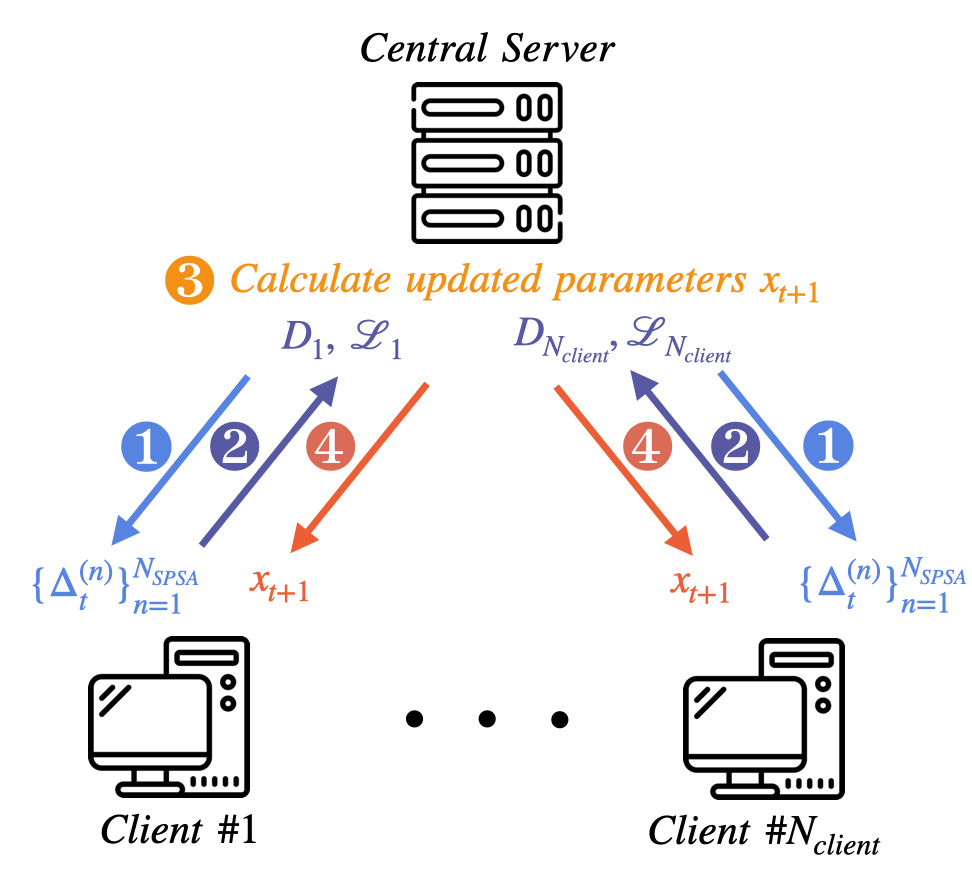

Resource-efficient and robust quantum federated learning via loss aggregation

Cheng-En Tsai, Hao-Chung Cheng

Submitted

A novel method that aggregates loss values instead of gradients in quantum federated learning, reducing communication overhead and quantum measurements by orders of magnitude while maintaining strong convergence under non-IID data distribution.

QSyn: A Developer-Friendly Quantum Circuit Synthesis Framework for NISQ Era and Beyond

Mu-Te Lau, Chin-Yi Cheng, et al., including Cheng-En Tsai and Chung-Yang (Ric) Huang

Developed a C++-based quantum circuit compilation framework that provides a unified environment for prototyping and evaluating quantum circuit synthesis algorithms, with robust developer tools including CI/CD and regression testing.

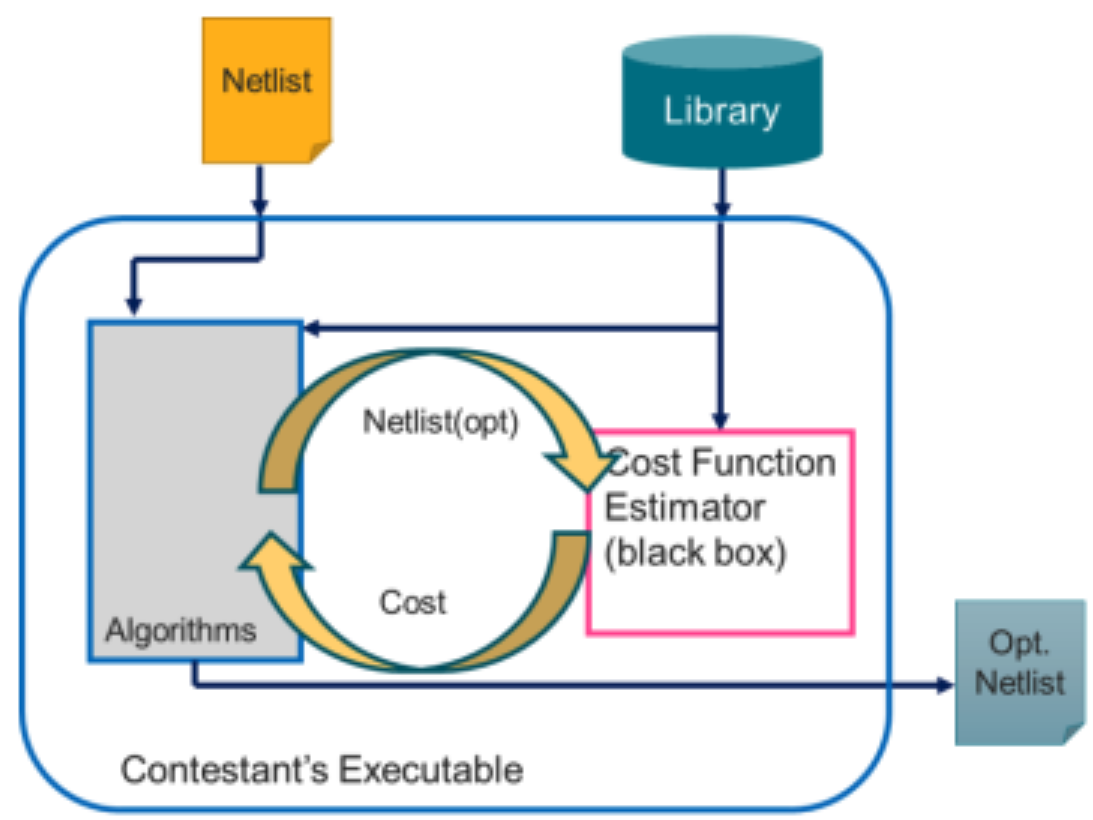

Reinforcement Logic Optimization for a General Cost Function

Apr 2024 – Jun 2024

Electronic Design Automation

- Developed a program to optimize digital circuits based on a black-box cost estimator, addressing complex optimization beyond traditional PPA metrics.

- Implemented the A2C reinforcement learning algorithm and Simulated Annealing on Yosys-ABC for circuit optimization, achieving up to 55.3% improvement in loss compared to the Greedy algorithm.

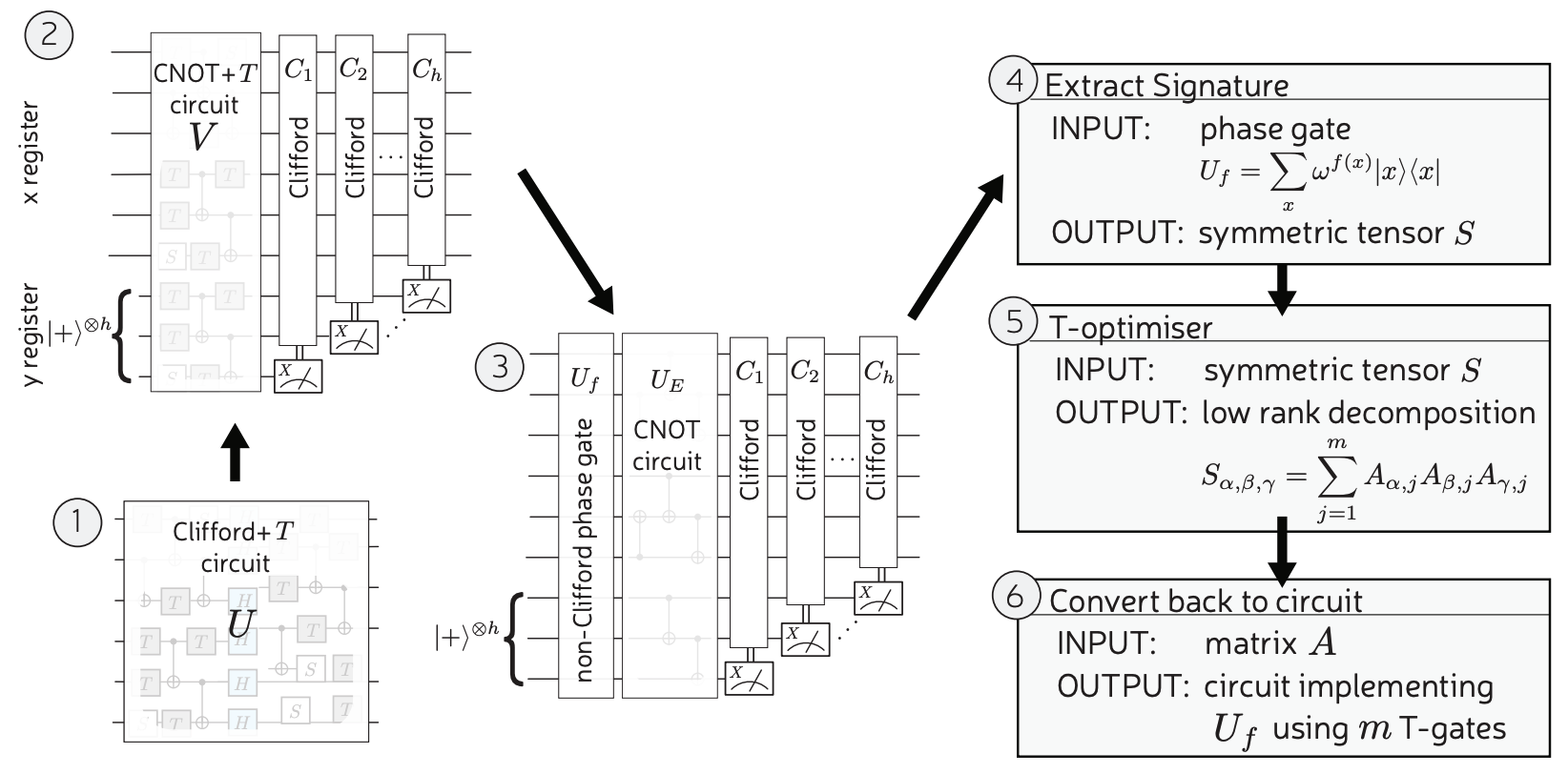

T-Count Optimization Framework for Clifford+T Quantum Circuits

Apr 2024 – Jun 2024

Quantum Information and Computation

- Developed a unified T-count optimization framework that integrates multiple reduction techniques including TMerge, Internal-H-OPT and advanced phase polynomial methods such as TODD for efficient circuit synthesis.

- Enhanced overall circuit efficiency by combining Gray synthesis (GraySyn) with T-parallelism (T-Par) strategies to exploit structural regularities and gate-level concurrency.

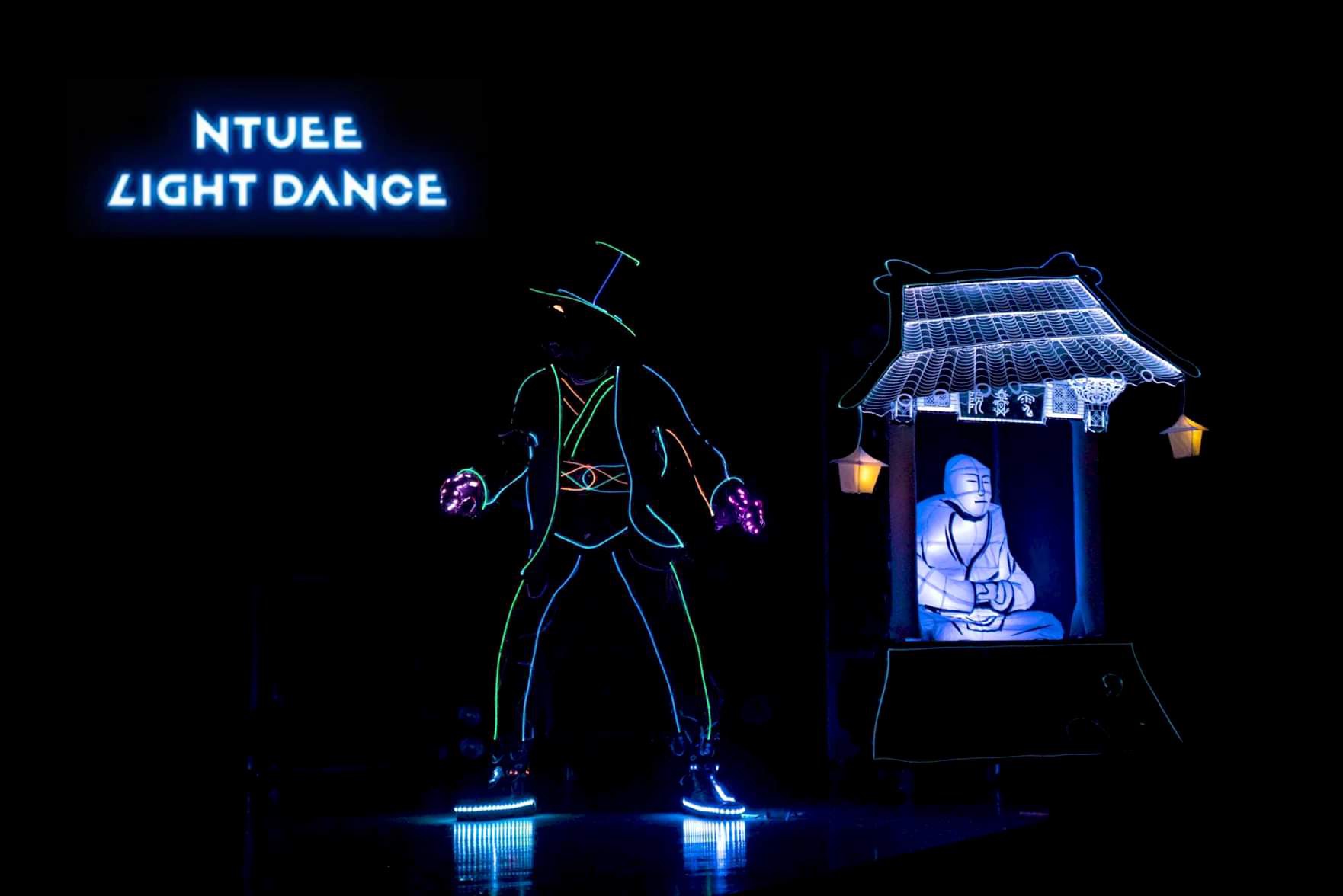

NTUEE LightDance

Oct 2022 – Mar 2024

Hardware Group: Manages electrical-related hardware & LightDancer

- Established a C/C++ library for the communication between ATTiny85 board and RPI.

- Constructed the full data path from the latch to the microcontroller and then to the Raspberry Pi for WS2812 LED strips, and from the PCA9955 IC to the Raspberry Pi for optical fiber.